ARQUITECTURA

vs MICROARQUITECTURA

La

arquitectura de un ordenador está constituida por la arquitectura de su

conjunto de instrucciones o ISA (del inglés Instruction Set Architecture)

y su microarquitectura.

Arquitectura del ordenador =

Arquitectura del conjunto de instrucciones (ISA) + Microarquitectura

La arquitectura

del conjunto de instrucciones (ISA) es una imagen abstracta del sistema de

computación tal como sería visto por un programador en lenguaje máquina, e

incluye el conjunto de instrucciones, modos de direccionamiento, registros y

formatos de direcciones y datos soportados por el procesador o CPU (del inglés Central

Processing Unit).

Los

procesadores, y por extensión los ordenadores, quedan definidos por tanto en

base a la arquitectura del conjunto de instrucciones que implementan, así

podemos encontrar referencias a procesadores u ordenadores de tipo CISC, RISC o

SISC:

- CISC (Complex Instruction Set Computer).

- RISC (Reduced Instruction Set Computer).

- SISC (Specific Instruction Set Computer).

En

arquitectura de computadoras, 16 bits, 32 bits o 64 bits es un adjetivo

usado para describir enteros, direcciones de memoria u otras unidades de datos

que comprenden hasta 16 bits, 32 bits o 64 bits de ancho. En el tema que nos

ocupa, se utilizan para referirse a una arquitectura de procesador basadas en

registros, bus de direcciones o bus de datos que permiten procesar (interna y

externamente) datos de ese ancho.

Diferentes

familias de procesadores pueden tener diferentes ISA, por este motivo, un

programa compilado para un tipo de máquina no podrá ejecutarse en otra con un

conjunto de instrucciones diferentes. Del mismo modo, un procesador con una

arquitectura de 32 bits no podrá ejecutar un sistema operativo u otra

aplicación compilada para una arquitectura/procesador de 64 bits. Sin embargo,

por compatibilidad hacia atrás, lo inverso suele ser posible, es decir, podemos

ejecutar aplicaciones de 32 bits en procesadores de 64 bits.

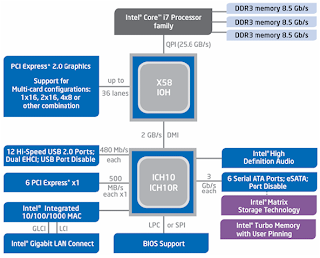

La microarquitectura,

en cambio, es de nivel más inferior, más concreto. Muestra las partes constituyentes

del sistema y cómo se interconectan e interoperan, para así implementar la

especificación de la arquitectura. La microarquitectura generalmente es

representada empleando un diagrama de bloques que describe las interconexiones

entre registros, buses y bloques funcionales de la máquina.

Diferentes

ordenadores podrían tener una misma arquitectura del conjunto de instrucciones,

y así ser capaces de ejecutar los mismos programas, sin embargo, pueden tener

diferentes microarquitecturas. Esas diferentes microarquitecturas (junto con

los avances en las tecnologías de fabricación de semiconductores) son las que

permiten nuevas generaciones de procesadores que permiten alcanzar mejores

niveles de rendimiento o performance

comparadas con las generaciones previas.

TRADE-OFF

La Teoría

del Trade-Off tiene sus orígenes en las teorías de la toma de decisión,

fundamentalmente en el concepto de optimalidad paretiana, que conduce al

concepto de tasa de intercambio (o Trade-Off) entre dos criterios. El Trade Off

indica en cuánto varía un criterio para lograr un incremento unitario en otro

criterio.

Cuando se

está en presencia de un problema, por lo general se da un conflicto entre

objetivos o cualidades versus costos o defectos; es por eso que en un proceso

de toma de decisiones es necesario tener una visión holística del hecho, con la

finalidad de considerar todos los elementos que involucren la decisión.

Normalmente, al analizar un problema lo abordamos desde el punto de vista

cualitativo, para ello quien toma las decisiones se basa fundamentalmente en

considerar sus experiencias previas en la solución de problemas semejantes. En

la medida en que el problema sea demasiado complejo o el tomador de decisiones

no tenga experiencias previas, resulta útil la realización de un análisis

cuantitativo, esto no significa que se deba soslayar la importancia de contar

con ambos puntos de vista para tomar la mejor decisión posible, pues al

considerarse se maximiza la efectividad en la toma de decisiones final

UNIFICACION DEL SET

DE INSTRUCCIONES

El ISA marca la

división entre el hardware y el software.

Incluye aquellos

aspectos visibles por un programa de aplicación o puede incluir aquellos

aspectos visibles sólo por el sistema operativo.

Al unir más de una

instrucción en forma lógica y coherente, se crea un programa.

Mediante el uso de

estos, la computadora es capaz de recibir, procesar y almacenar información. En

otras palabras, una computadora no es útil si no tiene un programa que le

indique lo que tiene que hacer.

Actualmente china esta desvalorando la unificación de

instrucciones:

Con más de mil trescientos millones de

habitantes y un sistema de gobierno comunista no sorprende la noticia. Como ya

ha ocurrido en otras ocasiones, China

busca un conjunto de instrucciones estándar. Un conjunto de

instrucciones, definido por las siglas ISA en inglés,

son aquellas operaciones de bajo nivel que son capaces de ejecutar los

microprocesadores y sobre las que se implementan soluciones como los sistemas

operativos.

La búsqueda de un conjunto de

instrucciones nacionales parece

no gustar a las compañías desarrolladoras como ARM. Pero más allá de la unificación de hardware, el

siguiente paso de la evolución podría seguir por una nacionalización del

software que impusiera funcionalidades y estándares.

Y es que el gobierno chino espera que

ese nuevo conjunto de instrucciones evite

la dependencia de propiedad intelectual situada fuera de sus fronteras.

Parece que son pasos que van hacia una dirección totalmente contraria a lo que

se venía viendo, no obstante son noticias importantes que merece la pena seguir

con detenimiento.

Ventajas

Compatibilidad entre

arquitecturas

Mayor facilidad de

aprender el set de instrucciones, que sería universal

Capacidad de migrar de

arquitectura sin problemas

Desventajas

Surgimiento de problemas

de intereses de las empresas fabricantes de dispositivos haciendo que el avance

tecnológico sea lento.

Estancamiento en la

creación de nuevas arquitecturas.

PROCESADORES CON LA MISMA ARQUITECTURA Y MICROARQUITECTURA

Los futuros microprocesadores Intel

Core de cuarta generación, basados en la nueva microarquitectura Haswell harán

su aparición entre abril a septiembre del próximo año; y hasta el momento sólo

conocemos muy pocas de sus nuevas características:

Un rendimiento por ciclo (IPC) 10% mayor que el de Ivy Bridge.

Un rendimiento por ciclo (IPC) 10% mayor que el de Ivy Bridge.

Un IGP que triplica la potencia

gráfica del IGP de Ivy Bridge.

Traerá las nuevas instrucciones AVX

2.0.

Fabricados con el proceso de manufactura

a 22nm Tri gate.

Las versiones para escritorio usarán

el nuevo socket LGA 1150 (no compatible con el actual LGA 1155).

La espera por conocer el resto de sus especificaciones llegará a su fin el próximo mes durante el evento Intel Developer Forum (IDF) 2012, el cual se realizará del 11 al 13 de septiembre de este año, y en el cual Intel revelará las especificaciones de muchos de sus actuales y futuros productos, entre ella las de los esperados microprocesadores basados en la micro-arquitectura Haswell.

Intel nos adelanta que detallará sus nuevas instrucciones AVX 2.0 (Intel se refiere a ellas como instrucciones vectoriales de segunda generación), TSX (Transactional Synchronization eXtensions) y BMI (Bit Manipulation Instructions, esta última ya presente en los microprocesadores AMD basados en las micro-arquitecturas Bulldozer, Piledriver y Jaguar).

Por el momento a modo de adelanto revelan que el nuevo IGP de Haswell tiene por nombre código Denlow y será compatible con las API DirectX 11.1, OpenGL 3.2, OpenCL entre otras nuevas características.

Hasta el momento sabemos que los microprocesadores

Intel Core de cuarta generación, basados en la micro-arquitectura Haswell

tendrán un masivo IGP con un rendimiento gráfico que triplica al de los

actuales IGP HD Graphics 4000, el IGP de mayor potencia gráfica de los actuales

microprocesadores Ivy Bridge-DT/MB/ULV.

Nuevamente desde Fudzilla nos informan que gracias a las muchas mejoras que poseerá la nueva micro-arquitectura Haswell, los futuros microprocesadores Core de cuarta generación: Haswell-DT/MB/ULT/E/EN/EP/EX tendrán un rendimiento por ciclo 10% superior que el de sus actuales equivalentes basados en la micro-arquitectura Ivy Bridge.

Nuevamente desde Fudzilla nos informan que gracias a las muchas mejoras que poseerá la nueva micro-arquitectura Haswell, los futuros microprocesadores Core de cuarta generación: Haswell-DT/MB/ULT/E/EN/EP/EX tendrán un rendimiento por ciclo 10% superior que el de sus actuales equivalentes basados en la micro-arquitectura Ivy Bridge.

Estas cifras se basan en las estimaciones realizadas con los ejemplares preliminares/prototipos (o muestras de ingeniería) basados en Haswell. Se espera también que la versión fianl del chip ofrezca una mayor personalización, permitiendo que los usuarios avanzados puedan lograr un mayor overclock.

Gráficos integrados Intel de próxima generación serán un 300% más rápidos

La arquitectura de cuarta generación Haswell para plataformas Intel Core está a la vuelta de la esquina, buscando reemplazar lo antes posible a la actual Ivy Bridge y sus gráficos HD 4000, denominados internamente como GT2, mientras que los HD Graphics 2500 corresponden a GT1.

Ya sabíamos que Intel prepara el venidero GT3 para poner a la par de CPUs Haswell, del que habíamos oído que rendiría hasta 2.5 veces más que GT2, sin embargo, nuevas filtraciones ahora revelan que el alza en desempeño será aún mejor, mostrándose al menos tres veces más rendidores que la generación anterior.

Para Intel, esto significaría una revolución y un cambio importante de paradigma en relación a su política de desarrollo anterior, donde el mayor énfasis se lo lleva la CPU y los gráficos quedaban en segundo plano, dándole prioridad en ese sentido al ahorro energético y además, sufriendo de una microarquitectura para IGP que sigue en pañales.

GT3 podría ser una respuesta más madura de Intel, que tampoco puede esperar competir contra NVIDIA y AMD de un día para otro, especialmente considerando que ambas compañías están haciendo esfuerzos para quitar tanta prioridad al procesador central y enfocarse más en los gráficos integrados, NVIDIA por el lado de los móviles y AMD haciendo lo suyo con las APU para PC.